Инструменты пользователя

4. Временные диаграммы машинных циклов

Содержание

Обработка команд программы микропроцессором Z80 представляет собой поэтапное выполнение следующих машинных циклов:

- извлечение кода операции (цикл M1);

- цикл чтения/записи памяти;

- цикл ввода/вывода;

- цикл предоставления доступа к шине;

- цикл подтверждения маскируемого прерывания;

- цикл подтверждения немаскируемого прерывания;

- выполнение команды останова.

Все команды состоят из последовательности машинных циклов. Каждый из этих машинных циклов продолжается от 3 до 6 тактов и может быть удлинён путём введения дополнительных тактов TW (время ожидания), если скорость ЦП ограничивается быстродействием внешнего устройства.

Рис. 4.1 показывает, что команды, как правило, состоят из 3 машинных циклов. Первый машинный цикл каждой команды — это цикл извлечения кода операции, который длится 4, 5 или 6 тактов синхронизации (если он не продлевается сигналом /WAIT), в цикле M1 из памяти извлекается код команды, которая потом выполняется. В последующих машинных циклах осуществляется передача данных между ЦП и памятью или устройством ввода–вывода. Эти цикли продолжаются от 3 до 6 тактов и также могут быть продлены сигналом /WAIT, если ЦП должен синхронизироваться с внешним устройством.

Далее рассматриваются временные диаграммы базовых машинных циклов. Очередность их выполнения, а также точное время выполнения команд (в тактах) приведены в 5.4.

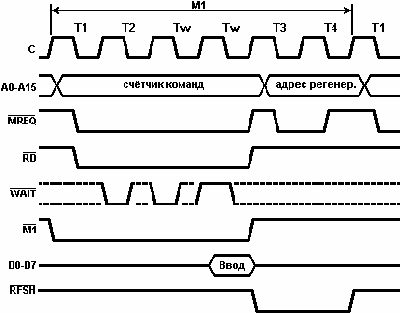

4.1. Извлечение кода операции

На рис.4.2 отражены временные процессы цикла M1. Содержимое счётчика команд PC (адрес кода операции в памяти) подается на шину адреса непосредственно в начале машинного цикла. Через полтакта (когда адрес памяти стабилизируется на шине) активизируется сигнал /MREQ. Его спадающий фронт прямо используется для выбора микросхемы запоминающего устройства. Одновременно с этим включается сигнал /RD и позволяет передать данные из памяти на шину данных ЦП. По нарастающему фронту такта T3 данные вводятся в ЦП. Этот же фронт используется и для выключения сигналов /MREQ и /RD

Во время тактов T3 и T4 происходит дешифрация и выполнение извлеченной команды внутри МП. Одновременно с этим производится регенерация динамической памяти: на 7 младших битов шины адреса подается адрес регенерации, и активизируется сигнал /RFSH указывая на то, что ША содержит адрес регенерации. Само восстановление происходит по сигналу /MREQ; сигнал RFSH нельзя использовать для этого, т.к. Устойчивость адреса регенерации обеспечивается только ко времени включения /MREQ. Во время регенерации сигнал /RD не формируется, чтобы избежать передачи данный из различных областей памяти на шину данных.

Рис. 4.2. Извлечение кода операции (цикл M1)

На рис.4.3 показано, как продлевается цикл извлечения кода операции, если память активизирует линию /WAIT. Во время спадающего фронта такта T2 и каждого последующего такта Tw ЦП анализирует линию /WAIT. Если она активна, то микропроцессор вырабатывает дополнительный такт ожидания Tw. Т.е. цикл считывания продолжается сколь угодно долго и приводится в соответствие со временем доступа к любой памяти.

Рис. 4.3. Извлечение кода операции (цикл M1) с тактами ожидания

4.2. Цикл чтения памяти и цикл записи в память

На рис. 4.4 показаны временные процессы циклов чтения из памяти и записи в память. Длительность этик циклов 3 такта, если не активизирована линия /WAIT. Сигналы /MREQ и /RD используются так же, как в цикле M1. В обоих циклах сигнал /MREQ активизируется, когда уровни сигналов на шине адреса стабилизировались, поэтому его спадающий фронт используется для выбора микросхемы ЗУ. В цикле записи линия /WR активизируется, когда данные на шине данных уже стабилизировались, т. о. этот сигнал непосредственно используется как импульс записи для всех типов полупроводниковой памяти. Он выключается на полтакта до изменения содержимого ША и ШД, что удовлетворяет параметрам всех типов полупроводниковых ОЗУ.

Рис. 4.4. Цикл чтения из памяти и цикл записи в память

На рис. 4.5 показано, как запрос /WAIT продлевает операцию чтения или записи в память. Это происходит так же, как в цикле M1.

Рис. 4.5. Цикл чтения из памяти и цикл записи в память с тактами ожидания

4.3. Циклы ввода/вывода

На рис. 4.6 изображены временные диаграммы циклов ввода–вывода.

При вводе/выводе содержимое шины адреса различно для двух случаев:

- Команды IN А,(п) и OUT (n),A:

- A0–A7 — содержит адрес канала (n)

- A8–A15 — содержимое аккумулятора

- Команды IN r,(C), INI, INIR, IND, INDR и OUT (C),r, OUTI, OTIR, OUTD, OTDR:

- A0–A7 — Содержимое регистра C

- A8–A15 — содержимое регистра B1)

Важно отметить, что в операциях ввода–вывода автоматически вводится такт ожидания Tw*, потому что время от включения сигнала /IORQ до момента опроса линии ожидания центральным процессором недостаточно для декодирования адреса устройства ввода–вывода и активизации им линии /WAIT. Во время этого такта также опрашивается линия ожидания, что даёт возможность согласовать работу ЦП с работой любых медленно действующих устройств. В операции ввода сигнал /RD используется для передачи данных адресованного канала на шину данных ЦП, как и при чтении памяти. В операциях вывода сигнал /WR используется как строб записи. Он выключается за полтакта до изменения состояния ША и ШД. что обеспечивает надежность записи в канал.

Рис. 4.6. Цикл ввода и цикл вывода

На рис. 4.7 изображены циклы ввода/вывода с дополнительными тактами ожидания.

4.4. Цикл предоставления доступа к шине

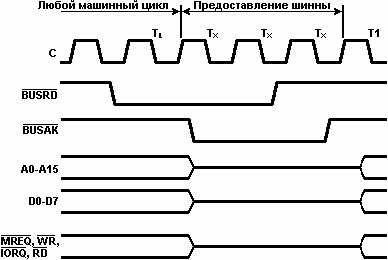

Рис. 4.8 отражает временные диаграммы запроса на доступ к шине и цикла подтверждения запроса. Сигнал /BUSRQ воспринимается ЦП во время нарастающего фронта последнего такта каждого машинного цикла. Если он имеет активный низкий уровень, то во время нарастающего фронта следующего тактового импульса (т.е. по окончании цикла) ЦП переводит шины адреса и данных, а также трехстабильные Сигналы управления в высокоомное состояние и активизирует сигнал подтверждения /BUSAK. Т.е. максимальное время до предоставления шины равно длительности машинного цикла (если запрос поступил в начале этого цикла).

Теперь внешнее устройство, запросившее доступ, может управлять шинами и передавать данные между памятью и УВВ. Этот режим называется прямым доступом к памяти (ПДП — DMA — Direct Memory Access). Его нельзя прервать ни сигналом /INT, ни /NMI.

Внешнее устройство поддерживает сигнал /BUSRQ в активном состоянии столько времени, сколько необходимо ему для прямого доступа. Состояние /BUSRQ анализируется процессором по нарастающему фронту каждого тактового импульса. Как только зафиксирован неактивный уровень /BUSRQ, со следующего такта управление шинами возвращается ЦП, и он возобновляет нормальную обработку команд.

Следует помнить, что во время длительных циклов ПДП (например, в случае пересылки больших блоков данных) и при использовании динамического ЗУ регенерацию должно осуществлять внешнее устройство.

4.5. Цикл подтверждения маскируемого прерывания

На рис.4.9 показаны временные процессы при запросе и подтверждении прерывания.

Сигнал прерывания /INT опрашивается ЦП во время нарастающего фронта последнего такта в конце каждой команды. Запрос игнорируется, если триггер разрешения прерывания сброшен или активен сигнал /BUSRQ. Если запрос воспринимается, то ЦП вырабатывает специальный цикл M1, в котором активизируется сигнал /IORQ (вместо /MREQ). Низкий уровень сигнала /IORQ указывает устройству, запросившему прерывание, что оно может подать на шину данных 8 разрядный вектор прерывания. В этот цикл автоматически включаются два такта ожидания Tw* (это позволяет сравнительно легко реализовать схему приоритетных прерываний), которые дают необходимое время для определения запросившего устройства и стабилизации вектора прерывания на шине данных.

Рис. 4.9. Цикл подтверждения маскируемого прерывания

Кроме двух обязательных тактов ожидания активным сигналом /WAIT могут быть введены дополнительные такты ожидания, что отражено на рис. 4.10.

Рис. 4.10. Цикл подтверждения маскируемого прерывания с тактами ожидания

4.6. Цикл подтверждения немаскируемого прерывания

На рис. 4.11 показан цикл запроса/подтверждения немаскируемого прерывания.

Информация о запросе /NMI анализируется одновременно с сигналом /INT (подробнее см. 6.2), но /NMI имеет более высокий приоритет и его нельзя запретить программно. Назначение /NMI — немедленное реагирование ЦП на внешние события (например, отказ питания). Ответ ЦП сходен с обычным циклом M1, с той лишь разницей, что шина данных игнорируется, т. к. при NMI ЦП выполняет повторный запуск с адреса 66H и вектор прерывания не нужен.

В цикле подтверждения NMI сигнал /WAIT не воспринимается.

4.7. Выполнение команды останова

Команда HALT вводит МП в состояние останова. Каждый цикл в состоянии останова представляет собой обычный цикл M1 с той лишь разницей, что извлекаемые из памяти данные игнорируются, и внутренне процессор формирует команду NOP. Холостые команды выполняются в целях поддержания процесса регенерации.

Сигнал /HALT своим активным уровнем сообщает, что ЦП находится в состоянии останова. Выход из этого состояния возможен только по прерыванию (маскируемому, если оно разрешено, или немаскируемому). Обе линии прерывания опрашиваются во время нарастающего фронта такта T4. как показано на рис. 4.12. Если прерывание воспринято, то следующий цикл будет циклом подтверждения прерывания.

Рис. 4.12. Выполнение команды останова