Инструменты пользователя

5. Система команд

Содержание

5.1. Методы адресации

Одним из важнейших показателей мощности системы команд любого микропроцессора является количество методов адресации. Под методом адресации понимается способ обращения команды к обрабатываемому операнду. Различные методы адресации необходимы, с одной стороны, для удобства программирования, с другой, для эффективной работы программ.

Далее рассмотрены методы адресации, используемые в системе команд МП Z80.

Непосредственная адресация.

При таком методе адресации операнд находится в памяти непосредственно за кодом операции команды. Он может быть 8 или 16–битной константой. Формат команд в этой случае:

┌───────────────────────────────────────┐ │ Код операции │ 1 или 2 байта ├────┬────┬────┬────┬────┬────┬────┬────┤ │ d7 │ d6 │ d5 │ d4 │ d3 │ d2 │ d1 │ d0 │ Операнд └────┴────┴────┴────┴────┴────┴────┴────┘ ┌───────────────────────────────────────┐ │ Код операции │ 1 или 2 байта ├────┬────┬────┬────┬────┬────┬────┬────┤ │ d7 │ d6 │ d5 │ d4 │ d3 │ d2 │ d1 │ d0 │ Младший байт операнда ├────┼────┼────┼────┼────┼────┼────┼────┤ │ d7 │ d6 │ d5 │ d4 │ d3 │ d2 │ d1 │ d0 │ Старший байт операнда └────┴────┴────┴────┴────┴────┴────┴────┘

Регистровая адресация.

В этом случае операнд находится в регистре либо в паре регистров ЦП. Регистр адресуется тремя битами, входящими в код операции, пара регистров — двумя.

Косвенная адресация.

При этой методе адресации операнд находится в ячейке памяти, адрес которой содержится в одной из регистровых пар ВС, DE или HL.

Абсолютная адресация.

За кодом операции в этом случае следуют два байта (16 бит), которые являются адресом. Это может быть адрес данных в памяти, адрес перехода или адрес подпрограммы.

┌───────────────────────────────────────┐ │ Код операции │ 1 или 2 байта ├────┬────┬────┬────┬────┬────┬────┬────┤ │ d7 │ d6 │ d5 │ d4 │ d3 │ d2 │ d1 │ d0 │ Младший байт операнда ├────┼────┼────┼────┼────┼────┼────┼────┤ │ d7 │ d6 │ d5 │ d4 │ d3 │ d2 │ d1 │ d0 │ Старший байт операнда └────┴────┴────┴────┴────┴────┴────┴────┘

Модифицированная нуль–страничная адресация.

Адресное пространство микропроцессора условно можно разбить на страницы по 4К. Тогда к нулевой странице будут относиться адреса 0000H…1000H. МП Z80 имеет специфический вид адресации, когда в коде операции 3 бита, задают модифицированный адрес рестарта. Эти адреса располагаются на нулевой странице области памяти МП. Команда состоит из одного байта:

┌────┬────┬────┬────┬────┬────┬────┬────┐ │ 1 │ 1 │ t5 │ t4 │ t3 │ 1 │ 1 │ 1 │ Код операции RST p └────┴────┴────┴────┴────┴────┴────┴────┘

А эффективный адрес рестарта будет:

0 0 0 0 0 0 0 0 0 0 t5 t4 t3 0 0 0 B,

или

00H, 08h, 10H, 18H, 20h, 28H, 30H и 38H.

Следующие три вида адресации МП Z80 существенно расширяют его возможности по сравнению с I8080.

Относительная адресация.

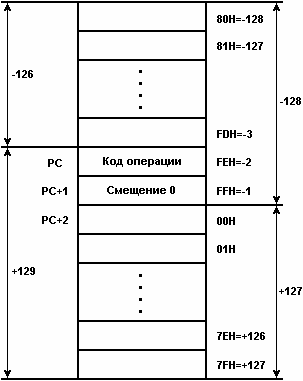

Этот вид адресации может использоваться командами условного и безусловного переходов. В каком случае они состоят из двух байтов: первый байт содержит код операции, а второй — смещение в дополнительном коде. Действительный адрес получается прибавлением смещения к текущему значению счетчика команд.

Смещение как число со знаком, может задаваться от -128 до +127. Но т.к. оно складывается с (РС+2), то фактически можно, адресоваться к ячейкам памяти, расположенным на расстоянии от -126 до +129 байт от адреса кода операции команды перехода.

Преимущества относительной адресации перед абсолютной:

- команда занимает в памяти на один байт меньше места;

- программа становится перемещаемой, т. е. не зависит от своего места расположения в памяти.

Индексная адресация.

Сущность индексной адресации аналогична относительной адресации, только в данном случае базой выступает не счётчик команд PC, а один из индексных регистров IX или IY. Данный метод адресации удобен при обработке массивов данный. Смещение d, непосредственно представленное в команде, складывается с содержимым индексного регистра и образует адрес памяти, по которому находятся данные. Т. е. можно адресоваться к данным находящимся в памяти на расстоянии от -128 до +127 байт от содержимого индексного регистра. Структура команд в данном случае:

┌─────────────────────────────┐ │ Управлявшее слово DD или FD │ ├─────────────────────────────┤ │ Код операции │ ├─────────────────────────────┤ │ Смещение d │ └─────────────────────────────┘

Битовая адресация.

Этот вид адресация используется в группе команд для работы с отдельными битами. Три разряда кода операции являются номером бита операнда, над которым будут производиться действия (тестирование, сброс или установка).

Встроенная адресация.

Некоторые команды, состоящие только из кода операции, однозначно определяют, где находится операнд. Например, команды работы с аккумулятором NEG и CPL.

Смешанная адресация.

Если в команде операнды адресованы по–разному, то имеет место смешанная адресация, например LD (IX+d),r

5.2. Группы команд

Систему команд МП можно разделить на группы команд в соответствии с их функциональным назначением. Группы команд представлены в таблицах 5.1.1 … 5.1.12.

Первая колонка в этих таблицах содержит символические обозначения (мнемокоды), используемые при написании программ на языке Ассемблера МП Z80. В основе этих символических обозначений, как правило, лежит аббревиатура полной записи команды на английском языке.

Во второй — время выполнения в тактах.

В третьей колонке приведены формат и двоичный кол команды.

Действия, происходящие при выполнении команды, показаны в четвертой колонке. Следует отметить, что здесь не отражен порядок выполнения этих действий; этот вопрос подробно рассмотрен в 5.4.

Последняя колонка отражает состояние флагов после выполнения команды.

В дальнейшем описании и таблицах приняты следующие обозначения:

| r | 8–битный регистр: A=111; B=000; C=001; D=010; E=011; H=100; L=101 | ||||||||||||||||

| dd qq pp rr | 16–битная регистровая пара:

|

||||||||||||||||

| n | 8–битный операнд | ||||||||||||||||

| nn | 16–битный операнд | ||||||||||||||||

| (nn) | содержимое ячейки nn (8–битный операнд) или содержимое ячеек nn и nn+1 (16–битный операнд) | ||||||||||||||||

| t | r, (HL), (IX+d) или (IY+d) | ||||||||||||||||

| e | t или n | ||||||||||||||||

| d | 8–битное смешение (-128 … +127) | ||||||||||||||||

| е | 8–битное смещение (-126 … +129) | ||||||||||||||||

| b | позиционный номер бита: D0=000; D1=001; D2=010; D3=011; D4=100; D5=101; D6=110; D7=111 |

||||||||||||||||

| cc | условие перехода: NZ=000 (не ноль); Z=001 (ноль); NC-010 (нет переноса); C=011 (перенос); PO=100 (нечетность); PE=101 (четность); P=110 (знак плюс); М=111 (знак минус) |

||||||||||||||||

| p | адрес рестарта: p=00H; p=08H; p=10H; p=18H; p=20H; p=28H; p=30H; p=38H |

||||||||||||||||

| a | номер рестарта: a=000; a=001; a=010; a=011; a=100; a=101; a=110; a=111 |

||||||||||||||||

| флаги | Состояние флагов:

|

||||||||||||||||

| T | число тактов за которое выполняется команда |

8–битовые команды загрузки.

Мнемоническое сокращение языка Ассемблера для всех команд загрузки одинаково: LD (load — загрузить). Далее следует указание приёмника, затем — указание источника пересылаемых данных.

LD приемник, источник

Таблица 5.1.1 содержит все команды 8–битной загрузки. Большую часть кодов в ней представляет команда LD r1,r2. В качестве r1 и r2 могут использоваться семь регистров: A, B, C, D, E, H и L, каждый из которых может служить как источником, так и приемником. Следовательно, эта команда дает в результате 49 кодов операции. В их числе семь команд с r1=r2, которые по действию аналогичны NOP, т.к. фактического переноса данных не происходит, и флаги не изменяются.

Источником переносимых данных может быть константа, непосредственно представленная в команде сразу за кодом операции. Команда в этом случае выглядит так:

LD r,n

Как источником, так и приёмником может служить память. Это даёт три типа команд:

LD r,(HL) LD (HL),r LD (HL),n

Память не может быть одновременно и источником, и приёмником пересылаемых данных; пересылка всегда происходит через ЦП.

С помощью управляющего слова DD либо FD предоставляется возможность использовать команды с индексным способом адресации. В этих командах за кодом операции следует смещение d.

LD r,(IX+d) LD r,(IY+d) LD (IX+d),r LD (IY+d),r LD (IX+d),n LD (IY+d),n

Эти команды не влияют на состояние флагов.

В следующих командах данные пересылаются между аккумулятором и ячейкой памяти, адресуемой абсолютно – (nn), либо косвенно через регистровую пару:

LD A,(BC) LD A,(DE) LD A,(nn) LD (BC),A LD (DE),A LD (nn),A

Флаги также остаются без изменений.

Регистры I и R могут использоваться как источник или приёмник в сочетании с аккумулятором:

LD A,I LD A,R LD I,A LD R,A

Команды LD A,I и LD A,R в отличим от всех остальных команд загрузки оказывают влияние на флаги:

- Н ← 0

- N ← 0

- P/V ← IFF2 (триггер разрешения /запрещения прерываний)

В сумме группа 8–битных команд загрузки содержит 104 различных кода.

16–битовые команды загрузки.

Команды этой группы представлены в таблице 5.1.2. В них возможна регистровая адресация и косвенная через указатель стека. Сюда же входят команды пересылки в стек и извлечения из стека, их мнемонические обозначения PUSH и POP соответственно. Отличие их от обычных команд загрузки состоит в том, что указатель стека автоматически уменьшается или увеличивается, когда байт «заталкивается» в стек или извлекается из стека. По действию команды PUSH и POP взаимно обратные. Это в равной степени относится и к последовательности обработки байтов (см. таблицу 5.3): при PUSH сначала обрабатывается старший байт, при POP — младший.

При всех 16–битовых командах загрузки, за исключением POP и AF не происходит изменения флагов.

16–битовые команды обмена.

Эта группа содержит 6 команд, которые изображены в таблице 5.1.8. Мнемоническое обозначение EX происходит от слова Exchange (обмен).

Команда EX AF,AF' дает возможность программным путем переключать пары регистров A, F и A', F'. А команда EXX позволяет переключаться на вспомогательный набор РОНов. Эти команды длиной всего один байт, и время, необходимое для переключения, сведено к минимальному. т.е. реализовано очень короткое время отклика на прерывание.

Как и 16–битовые команды загрузки, команды обмена не влияют на состояние флагов.

Команды обработки блоков.

Команды этой группы (см. таблицу 5.1.3) выполняют две функции пересылка блоков и поиск байта в блоке данных.

Команды пересылки имеют мнемоники:

| LDI | загрузка с инкрементом |

| LDIR | загрузка с инкрементом до BC=0 |

| LDD | загрузка с декрементом |

| LDDR | загрузка с декрементом до BC=0 |

Команда LDI (LDD) пересылает содержимое области памяти, начиная с адреса, указанного в HL в область памяти с начальным адресом в DE. Затем обе регистровые пары инкрементируются (декрементируются), и счётчик байтов BC уменьшается на 1.

Команда LDIR (LDDR) выполняется, так же как и LDI (LDD), только обработка сразу «зацикливается». Действие команды подобно пересылке блока данных при ПДП. Как для адресации, так и для счётчика байтов отведено по 16 бит, т.о. могут обрабатываться блоки любой длины и в любом месте памяти. Блоки данных могут также перекрываться. При HL=DE команда теряет смысл т.к. источник и приёмник идентичны. Следует обратить внимание, что при обработке команды сначала пересылаются данные, только затем декрементируется ВС, и на основании этого решается вопрос о цикличности команды, выполнять дальнейшую пересылку данных либо прекратить команду. После выполнения команды BC=0, что соответствует длине блока в 216 =65536 байт.

Выполнение этих команд влияет на флаги:

- Н ← 0

- N ← 0

- P/V ← 1, при циклическом выполнении команды до пересылки последнего байта

- P/V ← 0, когда результат декремента BC достигнет 0.

Поиск данных в блоке выполняют четыре команды:

| CPI | сравнение и инкремент |

| CPIR | сравнение и инкремент до BC=0 или A=(HL) |

| CPD | сравнение и декремент |

| CPDR | сравнение и декремент до BC=0 или A=(HL) |

При выполнении команды CPI (CPD) из содержимого аккумулятора вычитается содержимое ячейки памяти с адресом в HL, зятем декрементируется счетчик байтов BC, и инкрементируется (декрементируется) HL. В соответствии с результатом сравнения устанавливаются флаги.

Команда CPIR (CPDR) является цикличным повторением команды CPI (CPD) до тех пор, пока не выполнится одно из условий. Это либо нахождение идентичного байта, либо окончание просматриваемого блока. Соответственно этому устанавливаются флаги:

- S ← 1, когда результат сравнения отрицательный, иначе S ← 0

- Z ← 1, когда A=(HL), иначе Z ← 0

- H ← 1, когда был перенос в 4–й разряд, иначе Н ← 0

- P/V ← 1, при BC≠0

- P/V ← 0, когда результат декремента BC достигнет 0

- N ← 1

При каждом выполнении, до P/V=0, счётчик команд дважды декрементируется, что означает вновь обращение к этой команде.

8–битные арифметические и логические команды.

Команды этой группы отражены в таблице 5.1.4. Они всегда используют аккумулятор в качестве приёмника результата.

Следовательно, в команде указывается только источник. В совокупности в этой группе 108 различных кодов, которые имеют следующие мнемоники:

| ADD s | сложение |

| ADC s | сложение с учетом переноса |

| SUB s | вычитание |

| SBC s | вычитание с учетом переноса |

| AND s | логическое «И» |

| OR s | логическое «ИЛИ» |

| XOR s | «исключающее ИЛИ» |

| CP s | сравнение с аккумулятором |

| INC t | инкремент |

| DEC t | декремент |

Флаги C, Z, S и H устанавливаются соответственно результату операции. Флаги P/V действует в качестве флага переполнения V. Флаг N соответствует биту 4 кода выполняемой операции и указывает команде DAA (см. ниже), какая из арифметических операций выполнялась — сложение или вычитание.

Команда CP s выполняется так же, как и SUB s, c той разницей, что по результату операции лишь устанавливаются флаги, а содержимое аккумулятора не изменяется.

Отдельно можно выделить команды, в которых арифметические и логические операции производятся только над содержимым аккумулятора:

| ADD А | удвоение аккумулятора |

| ADC А | как ADD A с учётом переноса |

| SUB A | очистка аккумулятора (А←0), флаги: S←0, Z←1, H←0, P/V←0; N←1, C←0. |

| SBC A | как SUB А при C=0; когда C=1, содержимое аккумулятора сбрасывается в 0FFH. Флаги: S←1, Z←0, H←1, P/V←0; N←1, C←1. |

| AND А | аккумулятор остается без изменений; в соответствии с его содержимым устанавливаются флаги, S←старший бит; Z←1 при А=0, иначе Z←0; P/V←1 при чётном количестве единиц, иначе P/V←0; N←0; C←0. |

| OR A | как при AND A. |

| XOR А | очистка аккумулятора (A←00); флаги — как при AND A. |

| СР А | аккумулятор без изменений; флаги устанавливается как при SUB A. |

Общие операции с аккумулятором и флагами. К этой группе (таблица 5.1.4) относятся следующие 5 команд:

| DAA | десятичная коррекции аккумулятора |

| CPL | дополнение аккумулятора |

| NEG | инверсия аккумулятора |

| CCF | инверсии флага переноса |

| SCF | установка Флага переноса |

Десятичная коррекция аккумулятора используется после сложения либо вычитания чисел в BCD (двоично–десятичной) формате. В этом формате 8–битный операнд представляет собой двузначное десятичное число, в котором младшей десятичной цифре соответствует младшая тетрада, а старшей – старшая. Для цифр BCD формата допустимы значения от 0 до 9. Однако, результат сложения пли вычитания может превысить 9. В этом случае необходима десятичная коррекция. После команд сложения она действует следующим образом:

- если содержимое младшей тетрады аккумулятора больше 9 или H=1, то к аккумулятору добавляется число 6.

- если содержимое старшей тетрады аккумулятора стало после этого больше 9 или C=1, то число 6 добавляется и к старшей тетраде аккумулятора.

После вычитания:

- если H=1, то от аккумулятора вычитается число 6.

- если C=1, то число 6 вычитается и из старшей тетрады аккумулятора.

Команда CPL побитно инвертирует содержимое аккумулятора (дополнение до 1) Команда NEG изменяет знак содержимого аккумулятора на противоположный (дополнение до 2), она соответствует вычитанию содержимого аккумулятора из нуля. С помощью команды SCF флаг переноса устанавливается в 1, с помощью команды ССF его можно инвертировать.

16–битовые арифметические команды.

Команды этой группы сведены в таблицу 5.1.5. Их мнемоники соответствуют принятым для 8–битных арифметических команд, только дополнительно указывается приемник результата. 16–битные арифметические команды позволяют использовать регистровые пары и 16–разрядные регистры.

В этой группе не предусмотрена команда SUB, поэтому при потребности в ней следует применять команду SBC, предварительно сбросив флаг переноса, например, командой AND A.

Команды вращения и сдвига.

Эта группа команд объединена в таблице 5.1.11.

Эти команды позволяют адресоваться к любому регистру или ячейке памяти. Они особенно удобны при выполнении умножения и деления. Две команды (RLD и RRD) вращают тетрады аккумулятора и ячейки памяти, адресуемой парой HL. Их целесообразно применять в двоично–десятичной (BCD) арифметике. Конкретный вид вращения или сдвига ясен из символических пояснений к каждой команде. Эта группа содержит 76 команд.

Команды для работы с битами

Почти в каждой программе требуется возможность устанавливать, сбрасывать и проверять состояние, какого либо бита одного из регистров либо ячейки памяти. Такие биты в самом общем случае выполняют роль флагов, которые указывают программе какие предпринять действия. МП Z80 имеет команды, которые производят тестирование, установку и сброс любого бита регистра или ячейки памяти. Они сведены в таблице 5.1.7. При регистровой адресации действия производятся над аккумулятором или над одним из РОНов. При косвенной и индексной адресации действия производятся над памятью. При тестировании бита устанавливается флаг Z, если бит, равен нулю. Эта группа содержит 240 команд.

Команды переходов

Команды переходов собраны в таблице 5.1.6. Переход — это ветвление программы, при котором в счетчик команд PC загружается новый адрес. В команде он представлен абсолютно, относительно или косвенно. Следует помнить, что условный переход происходит только при выполнении условия, заданного в команде. Если условие не выполняется, то программа переходит к команде, следующей за командой перехода. При абсолютной адресации команда содержит адрес перехода. Такая команда состоит из трех байтов: кода операции, младшего байта адреса и старшего байта адреса перехода.

При относительной адресации команда состоит из двух байтов. Второй байт — это расстояние между адресом перехода и текущим состоянием счетчика команд (т.е. смешение). Смешение может быть от +127 до -126 относительно адреса кода операции команды, следующей за командой перехода.

При косвенной адресации в командах перехода содержим е регистровой пары HL пли одного из индексных регистр (IX или IY) прямо загружается в счетчик команд.

Для организации циклов в программе очень удобна команда DJNZ e. Эти двухбайтная команда перехода уменьшает содержимое регистра B на единицу, и если оно не стало равно нулю, то происходит переход на смешение e, заданное в команде.

Группа команд перехода не влияет на состояние флагов.

Команды вызова и возврата

Эта группа объединена в таблице 5.1.10. Команда вызова подпрограммы CALL — это специфическая команда перехода, при которой МП запоминает адрес команды, следующей за командой CALL. Команда возврата RET противоположна команде CALL. В ней адрес из стека прямо загружается в счётчик команд, и осуществляется возврат к прерванной программе. МП имеет две специальные команды возврата: RETI — возврат из маскируемого прерывания и RETN — возврат из немаскируемого прерывания. Команда RETI является единственной командой, которая распознается периферийными микросхемами комплекта Z80. Это необходимо для организации приоритетных прерываний и нормального возврата из прерываний, поступивших от периферийных схем. Об этом подробно написано в книге 7 «Построение систем. Программирование. Отладка».

Команды вызова подпрограмм состоят из 3 байтов. Однако, специфические команды рестарта RST p состоят из одного байта. Фиксированный адрес перехода встроен в код операции этих команд (см. методы адресации).

Группа команд вызова и возврата не влияет на состояние флагов.

Команды ввода–вывода

Набор команд ввода–вывода представлен в таблице 5.1.9. Адресация в этих командах может быть непосредственной либо косвенной, но регистру C.

Команды с непосредственной адресацией IN A,(n) и OUT (n),A аналогичны командам ввода–вывода МП I8080. Но в добавление к адресу порта n, выставляемому в младшую часть шины адреса, в старшую часть ША подается содержимое аккумулятора. Это позволяет, предварительно загрузив аккумулятор нужным значением, использовать 16–разридный адрес ввода–вывода. На флаги эти две команды не влияют.

В командах с косвенной адресацией данные пересылаются между портом адрес которого загружен в регистр C, и одним из РОНов.

IN r,(С) OUT (С), г

При этом в старшую часть адреса подается содержимое регистра B, т.е. также может использоваться 16–разрядный адрес ввода–вывода.

Две команды IN C,(C) и OUT (C),C имеют особенности. В команде вывода регистр C содержит адрес канала и его же в качестве данник посылает в порт. В команде ввода содержимое регистра C после ввода из порта замещается принятыми данными.

Команды OUT (C),r не влияют на флаги. Команды ввода IN r,(C) устанавливают флаги Z, S, P, H в соответствии с принятыми данными и сбрасывают флаг N. Следует уделить команду INF, которая, воздействуя на регистр флагов, не изменяет состояния РОН.

Косвенная адресация используется также командами ввода–вывода блоков. Они пересылают данные между портом, адресуемым регистром C, и памятью, адресуемой регистровой парой HL.

| INI | ввод и инкремент HL |

| INIR | ввод и инкремент HL до B=0 |

| IND | ввод и декремент HL |

| INDR | ввод и декремент HL по B=0 |

| OUTI | вывод и инкремент HL |

| OTIR | вывод и инкремент HL до B=0 |

| OUTD | вывод и декремент HL |

| OTDR | вывод и декремент HL до B=0 |

Регистр B здесь используется как двоичный счётчик — он автоматически декрементируется после пересылки каждого байта (максимально 256). Вместе с тем, содержимое B выдается в старшую часть ША. Это может быть использовано в случае, когда необходимо выводить данные в несколько портов с идущими подряд (в старшем байте) 16–разрядными адресами.

Команды ввода–вывода блоков устанавливают флаги следующим образом:

| S | неопределён |

| Z←1, если регистр B=0 (выполнение команд заканчивается), иначе Z←0 | |

| H | неопределён |

| P/V | неопределён |

| N←1 | не изменяется |

| C | |

Команды управления микропроцессором

Эта группа (таблица 5.1.12) содержит шесть команд управления.

Команда NOP — это пустая команда, при которой не выполняется никаких действий.

Команда HALT останавливает работу МП до тех пор, пока не будет принят запрос на прерывание. После выполнения команды HALT МП внутренне генерирует команды NOP, Чтобы производить регенерацию динамической памяти. Для работы с прерываниями служат команды DI и EI, которые запрещают и разрешают прерывания соответственно. МП может работать в одном из трёх режимов, прерывания, которые устанавливаются командами IM 0, IM 1 и IM 2 (подробнее см. главу 6).

Таблица 5.1.1. 8–битовые команды загрузки

| Команда | T | Код | Пояснения | C | Z | P | S | N | Y | ||

|---|---|---|---|---|---|---|---|---|---|---|---|

| LD r1,r2 | 4 | 01 | r1 | r2 | r1 ← r2 | ||||||

| LD r,(HL) | 7 | 01 | r | 110 | r ← (HL) | ||||||

| LD (HL),r | 7 | 01 | 110 | r | (HL) ← r | ||||||

| LD r,n | 7 | 00 - | r n | 110 - | r ← n | ||||||

| LD (HL),n | 10 | 00 - | 110 n | 110 - | (HL) ← n | ||||||

| LD r,(IX+d) | 19 | 11 01 - | 011 r d | 101 110 - | r ← (IX+d) | ||||||

| LD r,(IY+d) | 19 | 11 01 - | 111 r d | 101 110 - | r ← (IY+d) | ||||||

| LD {IX+d),r | 19 | 11 01 - | 011 110 d | 101 r - | (IX+d) ← r | ||||||

| LD {IY+d),r | 19 | 11 01 - | 011 110 d | 101 r - | (IY+d) ← r | ||||||

| LD (IX+d),n | 19 | 11 00 - - | 011 110 d n | 101 110 - - | (IX+d) ← n | ||||||

| LD (IY+d),n | 19 | 11 00 - - | 011 110 d n | 101 110 - - | (IY+d) ← n | ||||||

| LD A,(BC) | 7 | 00 | 001 | 010 | A ← (BC) | ||||||

| LD A,(DE) | 7 | 00 | 011 | 010 | A ← (DE) | ||||||

| LD A,(nn) | 13 | 00 - - | 111 n n | 010 - - | A ← (nn) | ||||||

| LD (BC),А | 7 | 00 | 000 | 010 | (BC) ← А | ||||||

| LD (DC),А | 7 | 00 | 010 | 010 | (DC) ← А | ||||||

| LD (nn),A | 7 | 00 - - | 110 n n | 010 - - | (nn) ← А | ||||||

| LD A,I | 9 | 11 01 | 101 010 | 101 111 | A ← I | ? | IF | ? | 0 | 0 | |

| LD A,R | 9 | 11 01 | 101 011 | 101 111 | A ← R | ? | IF | ? | 0 | 0 | |

| LD I,A | 9 | 11 01 | 101 000 | 101 111 | I ← A | ||||||

| LD R,A | 9 | 11 01 | 101 001 | 101 111 | R ← A | ||||||

Таблица 5.1.2. 16–битовые команды загрузки

| Команда | T | Код | Пояснения | C | Z | P | S | N | Y | ||

|---|---|---|---|---|---|---|---|---|---|---|---|

| LD dd,nn | 10 | 00 - - | dd0 n n | 001 - - | dd ← nn | ||||||

| LD IX,nn | 14 | 11 00 - - | 011 100 n n | 101 001 - - | IX ← nn | ||||||

| LD IY,nn | 14 | 11 00 - - | 111 100 n n | 101 001 - - | IY ← nn | ||||||

| LD HL,(nn) | 16 | 00 - - | 101 n n | 010 - - | H ← (nn+1) L ← (nn) | ||||||

| LD dd,(nn) | 20 | 11 01 - - | 101 dd1 n n | 101 011 - - | ddH ← (nn+1) ddL ← (nn) | ||||||

| LD IX,(nn) | 20 | 11 00 - - | 011 101 n n | 101 010 - - | IXH ← (nn+1) IXL ← (nn) | ||||||

| LD IY,(nn) | 20 | 11 00 - - | 111 101 n n | 101 010 - - | IYH ← (nn+1) IYL ← (nn) | ||||||

| LD (nn),HL | 16 | 00 - - | 100 n n | 010 - - | (nn+1) ← H(nn) ← L | ||||||

| LD (nn),dd | 20 | 11 01 - - | 101 dd0 n n | 101 011 - - | (nn+1) ← ddH (nn) ← ddL | ||||||

| LD (nn),IX | 20 | 11 01 - - | 011 100 n n | 101 010 - - | (nn+1) ← IXH (nn) ← IXL | ||||||

| LD (nn),IY | 20 | 11 01 - - | 111 100 n n | 101 010 - - | (nn+1) ← IYH (nn) ← IYL | ||||||

| LD SP,HL | 6 | 11 | 111 | 001 | SP ← HL | ||||||

| LD SP,IX | 10 | 11 11 | 011 111 | 001 001 | SP ← IX | ||||||

| LD SP,IY | 10 | 11 11 | 111 111 | 001 001 | SP ← IY | ||||||

| PUSH qq | 11 | 11 | qq0 | 101 | (SP-2) ← qqL (SP-1) ← qqH | ||||||

| PUSH IX | 15 | 11 11 | 011 100 | 101 101 | (SP-2) ← IXL (SP-1) ← IXH | ||||||

| PUSH IY | 15 | 11 11 | 111 100 | 101 101 | (SP-2) ← IYL (SP-1) ← IYH | ||||||

| POP qq | 10 | 11 | qq0 | 001 | qqH ← (SP+1) qqL ← (SP) | ||||||

| POP IX | 14 | 11 11 | 011 100 | 101 001 | IXH ← (SP+1) IXL ← (SP) | ||||||

| POP IY | 14 | 11 11 | 111 100 | 101 001 | IYH ← (SP+1) IYL ← (SP) | ||||||

Таблица 5.1.3. Команды обработки блоков

| Команда | T | Код | Пояснения | C | Z | P | S | N | Y | ||

|---|---|---|---|---|---|---|---|---|---|---|---|

| LDI | 16 | 11 10 | 101 100 | 101 000 | (DE) ← (HL) затем DE ← DE+1 HL ← HL+1 BC ← BC-1 | ? P=0, если BC-1=0 P=1, если BC-1≠0 | 0 | 0 | |||

| LDIR | 21 (16) | 11 10 | 101 110 | 101 000 | (DE) ← (HL) затем DE ← DE+1 HL ← HL+1 BC ← BC-1 и повтор до BC=0 | 0 | 0 | 0 | |||

| LDD | 16 | 11 10 | 101 101 | 101 000 | (DE) ← (HL) затем DE ← DE-1 HL ← HL-1 BC ← BC-1 | ? P=0, если BC-1=0 P=1, если BC-1≠0 | 0 | 0 | |||

| LDDR | 21 (16) | 11 10 | 101 111 | 101 000 | (DE) ← (HL) затем DE ← DE-1 HL ← HL-1 BC ← BC-1 и повтор до BC=0 | 0 | 0 | 0 | |||

| CPI | 16 | 11 | 101 | 101 | A-(HL)=? затем HL ← HL+1 ВС←ВС-1 | ? Z=1, если A=(HL) Z=0, если A≠(HL) | ? Р=0, если BC-1=0 Р=1, если BC-1≠0 | ? | 1 | ? | |

| CPIR | 21 (16) | 11 10 | 101 110 | 101 001 | A-(HL)=? затем HL ← HL+1 ВС←ВС-1 и повтор по BC=0 или A=(HL) | ? Z=1, если A=(HL) Z=0, если A≠(HL) | ? Р=0, если BC-1=0 Р=1, если BC-1≠0 | ? | 1 | ? | |

| CPD | 16 | 11 10 | 101 101 | 101 001 | A-(HL)=? затем HL ← HL-1 ВС←ВС-1 | ? Z=1, если A=(HL) Z=0, если A≠(HL) | ? Р=0, если BC-1=0 Р=1, если BC-1≠0 | ? | 1 | ? | |

| CPDR | 21 (16) | 11 10 | 101 111 | 101 001 | A-(HL)=? затем HL ← HL-1 ВС←ВС-1 и повтор по BC=0 или A=(HL) | ? Z=1, если A=(HL) Z=0, если A≠(HL) | ? Р=0, если BC-1=0 Р=1, если BC-1≠0 | ? | 1 | ? | |

Таблица 5.1.4. 8–битовые арифметические и логические команды

| Команда | T | Код | Пояснения | C | Z | P | S | N | Y | ||

|---|---|---|---|---|---|---|---|---|---|---|---|

| ADD A,r | 4 | 10 | 000 | r | A ← A+r | ? | ? | V | ? | 0 | ? |

| ADD A,n | 7 | 11 - | n | 110 - | A ← A+n | ? | ? | V | ? | 0 | ? |

| ADD A,(HL) | 7 | 10 | 000 | 110 | A ← A+(HL) | ? | ? | V | ? | 0 | ? |

| ADD A,(IX+d) | 19 | 11 10 - | 011 000 d | 101 110 - | A ← A+(IX+d) | ? | ? | V | ? | 0 | ? |

| ADD A,(IY+d) | 19 | 11 10 - | 111 000 d | 101 110 - | A ← A+(IY+d) | ? | ? | V | ? | 0 | ? |

| ADC A,s | 001 | A ← A+s+C | ? | ? | V | ? | 0 | ? | |||

| SUB s | 010 | A ← A-s | ? | ? | V | ? | 1 | ? | |||

| SBC A,s | 011 | A ← A-s-C | ? | ? | V | ? | 1 | ? | |||

| AND s | 100 | A ← A AND s | 0 | ? | P | ? | 0 | 1 | |||

| OR s | 110 | A ← A OR a | 0 | ? | P | ? | 0 | 0 | |||

| XOR s | 101 | A ← A XOR a | 0 | ? | P | ? | 0 | 0 | |||

| CP s | 111 | A-s=? | ? | ? | V | ? | 1 | ? | |||

| Код подставляется вместо 000 в командах | |||||||||||

| INC r | 4 | 00 | r | 100 | г ← r+1 | ? | V | ? | 0 | ? | |

| INC (HL) | 11 | 00 | 110 | 100 | (HL) ← (HL) + 1 | ? | V | ? | 0 | ? | |

| INC (IX+d) | 23 | 11 00 - | 011 110 d | 101 100 - | (IX+d) ← (IX+d)+1 | ? | V | ? | 0 | ? | |

| INC (IY+d) | 23 | 11 00 - | 111 110 d | 101 100 - | (IY+d) ← (IY+d)+1 | ? | V | ? | 0 | ? | |

| DEC t | 101 | t ← t-1 | ? | V | ? | 1 | ? | ||||

| Код подставляется вместо 100 в командах INC | |||||||||||

| DAA | 4 | 00 | 100 | 111 | Двоично–десятичная коррекция A | ? | ? | P | ? | ? | |

| CPL | 4 | 00 | 101 | 111 | A ← инверсия A | 1 | 1 | ||||

| NEG | 8 | 11 01 | 101 000 | 101 100 | А ← -А | ? | ? | V | ? | 1 | ? |

| CCF | 4 | 00 | 111 | 111 | C ← инверсия C | ? | 0 | X | |||

| SCF | 4 | 00 | 110 | 111 | C ← 1 | 1 | 0 | 0 | |||

Таблица 5.1.5. 16 битовые арифметические команды

| Команда | T | Код | Пояснения | C | Z | P | S | N | Y | ||

|---|---|---|---|---|---|---|---|---|---|---|---|

| ADD HL,dd | 11 | 00 | dd1 | 001 | HL ← HL+dd | ? | 0 | X | |||

| ADC HL,dd | 15 | 11 01 | 101 dd1 | 101 010 | HL ← HL+dd+C | ? | ? | V | ? | 0 | X |

| SBC HL,dd | 15 | 11 01 | 101 dd0 | 101 010 | HL ← HL-dd-C | ? | ? | V | ? | 1 | X |

| ADD IX,pp | 15 | 11 00 | 011 pp1 | 101 001 | IX ← IX+pp | ? | 0 | X | |||

| ADD IY,rr | 15 | 11 00 | 111 rr1 | 101 001 | IY ← IY+rr | ? | 0 | X | |||

| INC dd | 6 | 00 | dd0 | 011 | dd ← dd+1 | ||||||

| INC IX | 10 | 11 00 | 011 100 | 101 011 | IX ← IX+1 | ||||||

| INC IY | 10 | 11 00 | 111 100 | 101 011 | IY ← IY+1 | ||||||

| DEC dd | 6 | 00 | dd1 | 011 | dd ← dd-1 | ||||||

| DEC IX | 10 | 11 00 | 011 101 | 101 011 | IX ← IX-1 | ||||||

| DEC IY | 10 | 11 00 | 111 101 | 101 011 | IY ← IY-1 | ||||||

Таблица 5.1.6. Команды переходов

| Команда | T | Код | Пояснения | C | Z | P | S | N | Y | ||

|---|---|---|---|---|---|---|---|---|---|---|---|

| JP nn | 10 | 11 - - | 000 n n | 011 - - | PC ← nn | ||||||

| JP cc,nn | 10 | 11 - - | cc n n | 010 - - | PC ← nn, если условие выполняется PC ← PC+3, если нет | ||||||

| JR e | 12 | 00 - | 011 e-2 | 000 - | PC ← PC+e | ||||||

| JR C,e | 12 (7) | 00 - | 111 e-2 | 000 - | PC ← PC+e, еcли C=1 PC ← PC+2, если C=0 | ||||||

| JR NC,e | 12 (7) | 00 - | 110 e-2 | 000 - | PC ← PC+e, если C=0 PC ← PC+2, если C=1 | ||||||

| JR Z,e | 12 (7) | 00 - | 101 e-2 | 000 - | PC ← PC+e, если Z=1 PC ← PC+2, если Z=0 | ||||||

| JR NZ,e | 12 (7) | 00 - | 100 e-2 | 000 - | PC ← PC+e, если Z=0 PC ← PC+2, если Z=1 | ||||||

| JP (HL) | 4 | 11 | 101 | 001 | PC ← HL | ||||||

| JP (IX) | 8 | 11 11 | 011 101 | 101 001 | PC ← IX | ||||||

| JP (IY) | 8 | 11 11 | 111 101 | 101 001 | PC ← IY | ||||||

| DJNZ e | 13 (8) | 00 - | 010 e-2 | 000 - | B ← B-1, при B=0 PC ← PC+2 при B≠0 PC ← PC+e | ||||||

Таблица 5.1.7 Команды для работы с битами

| Команда | T | Код | Пояснения | C | Z | P | S | N | Y | ||

|---|---|---|---|---|---|---|---|---|---|---|---|

| BIT b,r | 8 | 11 01 | 001 b | 011 r | Z ← инверсия rb | ? | X | X | 0 | 1 | |

| BIT b,(HL) | 12 | 11 01 | 001 b | 011 110 | Z ← инверсия (HL)b | ? | X | X | 0 | 1 | |

| BIT b,(IX+d) | 20 | 11 11 - 01 | 011 001 d b | 101 011 - 110 | Z ← инверсия (IX+d)b | ? | X | X | 0 | 1 | |

| BIT b,(IY+d) | 20 | 11 11 - 01 | 111 001 d b | 101 011 - 110 | Z ← инверсия (IY+d)b | ? | X | X | 0 | 1 | |

| SET b.r | 8 | 11 11 | 001 b | 011 r | rb ← 1 | ||||||

| SET b,(HL) | 15 | 11 11 | 001 b | 011 110 | (HL)b ← 1 | ||||||

| SET b,(IX+d) | 23 | 11 11 - 11 | 011 001 d b | 101 011 - 110 | (IX+d) b ← 1 | ||||||

| SET b,(IY+d) | 23 | 11 11 - 11 | 111 001 d b | 101 011 - 110 | (IY+d) b ← 1 | ||||||

| RES b,t | 10 | t b ← 0 | |||||||||

| Код 10 подставляется вместо 11 в командах SET | |||||||||||

| Команда | T | Код | Пояснения | C | Z | P | S | N | Y | ||

|---|---|---|---|---|---|---|---|---|---|---|---|

| EX DE,HL | 4 | 11 | 101 | 011 | DE ↔ HL | ||||||

| EX AF,AF’ | 4 | 00 | 001 | 000 | AF ↔ AF’ | ||||||

| EXX | 4 | 11 | 011 | 001 | BC ↔ ВС’ DE ↔ DE’ HL ↔ HL’ | ||||||

| EX (SP),HL | 19 | 11 | 100 | 011 | H ↔ (SP+1) L ↔ (SP) | ||||||

| EX (SP),IX | 23 | 11 11 | 011 100 | 101 011 | IXH ↔ (SP+1) IXL ↔ (SP) | ||||||

| EX (SP),IY | 23 | 11 11 | 111 100 | 101 011 | IYH ↔ (SP+1) IYL ↔ (SP) | ||||||

Таблица 5.1.9. Команды ввода вывода

| Команда | T | Код | Пояснения | C | Z | P | S | N | Y | ||

|---|---|---|---|---|---|---|---|---|---|---|---|

| IN A,(n) | 11 | 11 - | 011 n | 011 - | A ← (n) ADR ← A/n | ||||||

| IN r,(C) | 12 | 11 01 | 101 r | 101 000 | r ← (C) ADR ← B/C | ? | P | ? | 0 | ? | |

| INF | 12 | 11 01 | 101 110 | 101 000 | F ← (C) ADR ← B/C F—регистр флагов | ? | P | ? | 0 | ? | |

| INI | 16 | 11 10 | 101 100 | 101 010 | (HL)←(C) ADR←B/C затем B ← B-1 HL ← HL+1 | ? Z=1, если B-1=0 Z=0, если B-1≠0 | X | X | 1 | X | |

| INIR | 21 (16) | 11 10 | 101 110 | 101 010 | (HL)←(C) ADR←B/C затем B ← B-1 HL ← HL+1 | 1 | X | X | 1 | X | |

| IND | 16 | 11 10 | 101 101 | 101 010 | (HL)←(C) ADR←B/C затем B ← B-1 HL ← HL-1 | ? Z=1, если B-1=0 Z=0, если B-1≠0 | X | X | 1 | X | |

| INDR | 21 (16) | 11 10 | 101 111 | 101 010 | (HL)←(C) ADR←B/C затем B ← B-1 HL ← HL-1 и повтор до B=0 | 1 | X | X | 1 | X | |

| OUT (n),A | 11 | 11 - | 010 n | 011 - | (n) ← A ADR ← A/n | ||||||

| OUT (C),r | 12 | 11 01 | 101 r | 101 001 | (C) ← r ADR ← B/C | ||||||

| OUTI | 16 | 11 10 | 101 100 | 101 011 | (C)←(HL) ADR←B/C затем B ← B-1 HL ← HL+1 | ? Z=1, если B-1=0 Z=0, если B-1≠0 | X | X | 1 | X | |

| OTIR | 21 (16) | 11 10 | 101 110 | 101 011 | (C)←(HL) ADR←B/C затем B ← B-1 HL ← HL+1 | 1 | X | X | 1 | X | |

| OUTD | 16 | 11 10 | 101 101 | 101 011 | (C)←(HL) ADR←B/C затем B ← B-1 HL ← HL-1 | ? Z=1, если B-1=0 Z=0, если B-1≠0 | X | X | 1 | X | |

| OTDR | 21 (16) | 11 10 | 101 111 | 101 011 | (C)←(HL) ADR←B/C затем B ← B-1 HL ← HL-1 и повтор до B=0 | 1 | X | X | 1 | X | 1 |

Таблица 5.1.10. Команды вызова и возврата

| Команда | T | Код | Пояснения | C | Z | P | S | N | Y | ||

|---|---|---|---|---|---|---|---|---|---|---|---|

| CALL nn | 17 | 11 - - | 001 n n | 101 - - | (SP-1) ← PC H (SP-2) ← PC L PC ← nn | ||||||

| CALL cc,nn | 17 (10) | 11 - - | cc n n | 100 - - | (SP-2) ← PC L PC←nn, если cc верно PC←PC+3, если нет | ||||||

| RET | 10 | 11 | 001 | 001 | PCL ← (SP) PCH ← (SP+1) | ||||||

| RET cc | 11 (6) | 11 | cc | 000 | PCL ← (SP) PCH ← (SP+1) PC ← PC+1, если cc не выполняется | ||||||

| RETI | 14 | 11 01 | 101 001 | 101 101 | Возврат из INT | ||||||

| RETN | 14 | 11 01 | 101 000 | 101 101 | Возврат из NMI | ||||||

| RST p | 11 | 11 | a | 111 | (SP-1) ← PCH (SP-2) ← PCL PC ← 0 PCL ← p | ||||||

Для некоторых команд в колонке T указано два значения — без скобок и в скобках:

- для условных команд JR, CALL, RET в скобках указано количество тактов выполнения команды при невыполнении условия;

- для «цикличных» команд DJNZ, LDIR, LDDR, CPIR, CPDR, INIR, INDR, OTIR. OTDR в скобках указано количество тактов, за которое выполняется команда в последний (перед завершением) раз.

Таблица 5.1.11. Команды сдвига и вращения

| Команда | T | Код | Пояснения | C | Z | P | S | N | Y | ||

|---|---|---|---|---|---|---|---|---|---|---|---|

| RLCA | 4 | 00 | 000 | 111 | ┌────────────────────┐ ┌───┐ │ ┌───────────────┐ │ │ C ├◄─┴─┤ A ├◄─┘ └───┘ └───────────────┘ | ? | 0 | 0 | |||

| RLA | 4 | 00 | 010 | 111 | ┌─────────────────────────────┐ │ ┌───┐ ┌───────────────┐ │ └─┤ C ├◄───┤ A ├◄─┘ └───┘ └───────────────┘ | ? | 0 | 0 | |||

| RRCA | 4 | 00 | 001 | 111 | ┌────────────────────┐

│ ┌───────────────┐ │ ┌───┐

└─►┤ A ├─┴─►┤ C │

└───────────────┘ └───┘

| ? | 0 | 0 | |||

| RRA | 4 | 00 | 011 | 111 | ┌─────────────────────────────┐

│ ┌───────────────┐ ┌───┐ │

└─►┤ A ├───►┤ C ├─┘

└───────────────┘ └───┘

| ? | 0 | 0 | |||

| RLC r | 8 | 11 00 | 001 000 | 011 r | ┌────────────────────┐ ┌───┐ │ ┌───────────────┐ │ │ C ├◄─┴─┤ t ├◄─┘ └───┘ └───────────────┘ | ? | ? | P | ? | 0 | 0 |

| RLC (HL) | 15 | 11 00 | 001 000 | 011 110 | ? | ? | P | ? | 0 | 0 | |

| RLC (IX+d) | 23 | 11 11 - 00 | 011 001 d 000 | 101 011 - 110 | ? | ? | P | ? | 0 | 0 | |

| RLC (IY+d) | 23 | 11 11 - 00 | 111 001 d 000 | 101 011 - 110 | ? | ? | P | ? | 0 | 0 | |

| RL t | 010 | ┌────────────────────────────┐ │ ┌───┐ ┌───────────────┐ │ └─┤ C ├◄──┤ t ├◄─┘ └───┘ └───────────────┘ | ? | ? | P | ? | 0 | 0 | |||

| RRC t | 001 | ┌────────────────────┐ │ ┌───────────────┐ │ ┌───┐ └─►┤ t ├─┴─►┤ C │ └───────────────┘ └───┘ | ? | ? | P | ? | 0 | 0 | |||

| RR t | 011 | ┌────────────────────────────┐ │ ┌───────────────┐ ┌───┐ │ └─►┤ t ├──►┤ C ├─┘ └───────────────┘ └───┘ | ? | ? | P | ? | 0 | 0 | |||

| SLA t | 100 | ┌───┐ ┌───────────────┐ │ C ├◄──┤ t ├◄─ 0 └───┘ └───────────────┘ | ? | ? | P | ? | 0 | 0 | |||

| SRA t | 101 | ┌─►──┐

│ ┌─┴─────────────┐ ┌───┐

└─◄┤ t ├──►┤ C │

└───────────────┘ └───┘

| ? | ? | P | ? | 0 | 0 | |||

| SRL t | 111 |

┌───────────────┐ ┌───┐

0 ─►┤ t ├──►┤ C │

└───────────────┘ └───┘

| ? | ? | P | ? | 0 | 0 | |||

| RLD | 18 | 11 01 | 101 101 | 101 111 | ┌───────►──────┐

┌────┬──┴─┐ ┌────┬─┴──┐

│ A │ │(HL) │

└────┴──┬─┘ └─┬┬─┴─┬──┘

└───◄─────┘└─◄─┘

| ? | P | ? | 0 | 0 | |

| RRD | 18 | 11 01 | 101 100 | 101 111 | ┌───►─────┐┌─►─┐

┌────┬──┴─┐ ┌─┴┴─┬─┴──┐

│ A │ │(HL) │

└────┴──┬─┘ └────┴─┬──┘

└───────◄──────┘

| ? | P | ? | 0 | 0 | |

Таблица 5.1.12. Команды управления микропроцессором

| Команда | T | Код | Пояснения | C | Z | P | S | N | Y | ||

|---|---|---|---|---|---|---|---|---|---|---|---|

| NOP | 4 | 00 | 000 | 000 | Нет операции | ||||||

| HALT | 4 | 01 | 110 | 110 | Останов | ||||||

| DI | 4 | 11 | 110 | 011 | Прерывания запрещены | ||||||

| EI | 4 | 11 | 111 | 011 | Прерывания разрешены | ||||||

| IM 0 | 8 | 11 01 | 101 000 | 101 110 | Режим прерывания 0 | ||||||

| IM 1 | 8 | 11 01 | 101 010 | 101 110 | Режим прерывания 1 | ||||||

| IM 2 | 8 | 11 01 | 101 011 | 101 110 | Режим прерывания 2 | ||||||

5.3. Флаги признаков

Каждый из двух флаговых регистров МП Z80 содержит по шесть информационных битов, состояние которых устанавливается в соответствии с результатом операции. Флаги S, Z, C и P/V используются в командах условного перехода, условного вызова подпрограмм и условного возврата из подпрограмм. Флаги H и N непосредственно программно не анализируются. Они используются в двоично–десятичной арифметике.

S (F7) Sign — Флаг знака

Этот Флаг предназначен для обработки чисел со знаком. Флаг устанавливается, когда результат операции отрицателен. Т.к. бит 7 является знаковым (любое отрицательное число содержит единицу в 7 бите), то этот флаг копирует состояние 7 бита аккумулятора.

При программировании состояние этого флага условно кодируется как P (Plus, знак плюс, S=0) и M (Minus, знак минус, S=1).

Z (F6) Zero — Флаг нуля

Флаг Z устанавливается или обнуляется в результате выполнения следующих команд:

- При 8–битных арифметических и логических операциях флаг устанавливается в 1, если результат выполнения команды равен нулю. Если результат не равен нулю, флаг Z обнуляется.

- При командах поиска и сравнения флаг Z устанавливается в 1. когда содержимое ячейки памяти адресуемой регистровой парой HL, совладает с содержимым аккумулятора.

- После выполнения команды тестирования отдельного бита во флаг Z записывается инвертированное значение проверенного бита.

- Если при выполнении команд INI, IND, OUTI, OUTD результат декремента (В-1) не равен нулю, то флаг Z=0. Когда результат (В-1)=0, флаг Z устанавливается.

- Флаг Z устанавливается в 1, когда в результате выполнения команд IN r,(C) содержимое регистра r обнуляется.

При программировании этот флаг следует условно кодировать как Z (Zero, результат равен нулю, Z=1) и NZ (No Zero, результат не равен нулю, Z=0)

C (F0) Carry — Флаг переноса

На состояние этого флага влияют следующие команды:

- Команды сложения устанавливают флаг C, когда есть Перенос от бита 7 к биту 8 результата сложения однобайтных чисел, или от бита 15 к биту 16 при сложении двухбайтных чисел. Иначе C=0.

- Команды вычитания устанавливают флаг, если есть заём, и сбрасывают, когда его нет.

- Команды RLA, RRA, RL t и RR t используют флаг C как бит связи между 7 и 0 битами.

- После выполнения команд RLCA, RLC t, SLA t флаг C копирует значение бита 7 операнда.

- После выполнения команд RRCA, RRC t, SRA t, SRL t флаг C копирует значение бита 0 операнда.

- Логические команды AND s, OR s и XOR s обнуляют флаг C.

- Команда SCF устанавливает флаг C, а команда CCF его инвертирует.

При программировании флаг кодируется как C (Carry, был перенос, C=1) и NC (No Carry, не было переноса, С=0)

P/V (F2) Parity/Overflow — Флаг чётности/переполнения

Этот флаг имеет несколько функций:

При арифметических операциях над числами со знаком он действует как флаг переполнения V. т.к. диапазон представления чисел со знаком от -128 до +127, то при операциях над ними возможен выход результата за эти пределы — переполнение. В этом случае флаг, устанавливается в 1, сигнализируя об ошибочности результата. Логика установки флага V в 1 такова:

- а) если был перенос из 6–го бита в 7–ой, и не было переноса из 7–го бита во флаг C.

- б) не было переноса из 6–го бита в 7–ой, но есть перенос из 7–го бита во флаг C.

Примеры:

- 1. Сложение

+76= 01001100 -114= 10001110 ──────── 11011010 = -38 верно C=0 V=0 - 2. Сложение

-1= 11111111 -1= 11111111 ──────── 11111110 = -2 верно С=1 V=0 - 3. Сложение

+82= 01010010 +94= 01011110 ──────── 10110000 = -80 неверно! C=0 V=1

В последнем примере произошла установка флага V. Это означает, что ошибка должна быть программно учтена при анализе результата.

- При выполнении логических операций, команд вращения и сдвига, а также команды IN r,(C) флаговый бит 2 действует как флаг чётности P. Он устанавливается, когда регистр содержит четное количество единиц, и обнуляется при нечетном количестве единиц.

- При выполнении команд LD A,I и LD A,R флаг P/V копирует состояние триггера прерываний IFF2, что позволяет в любое время узнать состояние процессора.

- Во время выполнения команд поиска CPI, CPIR, CPD и CPDR, а также команд пересылки блоков LDI, LPIR, LDD и LDDR флаг P/V=1, пока содержимое счётчика байтов (регистр BC) отлично от нуля. Когда BC=0, флаг P/V сбрасывается.

При программировании этот флаг условно кодируется как PO (Parity Odd, нечётно, P/V=0) и PE (Parity Even, чётно, P/V=1).

H (F4) Halfoarry — Флаг полупереноса

Команды сложения, вычитания, инкремента, декремента и сравнения 8–битных операндов устанавливают флаг H когда был перенос из третьего бита результата в четвертый, или был заём от четвёртого бита к третьему. Этим он указывает команде DAA требует ли результат десятичной коррекции.

N (F1) Addition/Subtraction — Флаг сложения/вычитания

Команды сложение, инкремента и логические команды обнуляют флаг N, а команды вычитания, декремента, сравнения и инвертирования его устанавливают.

Состояние флага N используется командой DAA. Т.к. алгоритм корректировки результата двоично–десятичных операций различен при сложении и вычитании, этот флаг показывает, какое именно действие происходило перед этим.

В таблице 5.2 показано как выполнение команд влияет на регистр флагов. Команды, которые здесь не представлены, не влияют ни на один флаг.

| Группа команд | Регистр флагов | Пояснения | |||||||

|---|---|---|---|---|---|---|---|---|---|

| F7 S | F6 Z | F5 \ | F4 H | F3 \ | F2 P/V | F1 N | F0 С |

||

| LD A,I; LD A,R | ? | ? | X | 0 | X | IF | 0 | P/V ← IFF2 | |

| LDI; LDD | X | X | X | 0 | X | ? | 0 | Если BC≠0, то P/V=1 Если BC=0, то P/V=0 |

|

| LDIR; LDDR | X | X | X | 0 | X | 0 | 0 | ||

| CPI; CPD; CPIR; CPDR | X | ? | X | X | X | ? | 1 | Если BC≠0, то P/V=1 Если BC=0, то P/V=0 Если A≠(HL), то Z=0 Если A=(HL), то Z=1 |

|

| ADD s; ADC s | ? | ? | X | ? | X | V | 0 | ? | 8–битовые арифметические команды |

| SUB s; SBC s; CP s; NEG | ? | ? | X | ? | X | V | 1 | ? | |

| AND s | ? | ? | X | 1 | X | P | 0 | 0 | Логические команды |

| OR s; XOR s | ? | ? | X | 0 | X | P | 0 | 0 | |

| INC t | ? | ? | X | ? | X | V | 0 | Только 8–битовые команды | |

| DEC t | ? | ? | X | ? | X | V | 1 | ||

| ADD HL,dd; ADD IX,pp; ADD IY,rr | X | X | X | 0 | ? | 16–битовые – арифметические команды | |||

| ADC HL,dd | ? | ? | X | X | X | V | 0 | ? | |

| SBC HL,dd | ? | ? | X | X | X | V | 1 | ? | |

| DAA | ? | ? | X | ? | X | P | ? | ||

| CPL | X | 1 | X | 1 | |||||

| CCF | X | X | X | 0 | ? | ||||

| SCF | X | 0 | X | 0 | 1 | ||||

| RLCA; RLA; RRCA; RRA | X | 0 | X | 0 | ? | Вращение аккумулятора | |||

| RLC t; RRC t; RL t; RR t; SLA t; SRA t; SRL t | ? | ? | X | 0 | X | P | 0 | ? | Группа команд вращения и сдвига |

| RLD; RRD | ? | ? | X | 0 | X | P | 0 | Перестановка тетрад Z ← инверсия sb | |

| BIT b,t | X | ? | X | 1 | X | X | 1 | ||

| IN r,(C); INF | ? | ? | X | ? | X | P | 0 | ||

| INI; IND; OUTI; OUTD | X | ? | X | X | X | X | 1 | Блочные команды ввода–вывода: Если B≠0, то Z=0 Если В=0, то Z=1 |

|

| INIR; INDR; OTIR; OTDR | X | 1 | X | X | X | X | 1 | ||

5.4. Очередность выполнения по циклам

Для обозначения действий микропроцессора в каждой машинном цикле в таблице 5.3 приняты следующие сокращения:

| OCR (operation code read) | чтение кода операции |

| CBR (control byte read) | чтение управляющего байта кода операции (ED, DD, FD, CB) |

| IOP (internal CPU operation) | внутренние операции ЦП, выходные сигналы управления неактивны |

| MRD (memory read) | чтение байта из косвенно адресованной ячейки памяти |

| MRH (memory rend, high byte) | чтение старшего байта 16–разрядного слова из косвенно адресованной ячейки памяти |

| MRL (memory read, low byte) | чтение младшего байта 16–разрядного слова из косвенно адресованной ячейки памяти |

| MWR (memory write) | запись байта в косвенно адресованную ячейку памяти |

| MWH (memory write, high byte) | запись старшего байта 16–разрядиого слова в косвенно адресованную ячейку памяти |

| MWL (memory write, low byte) | запись младшего байта 16–разрядного слова в косвенно адресованную ячейку памяти |

| ORD (operand read) | чтение операнда–байта, непосредственно представленного в команде |

| ORH (operand read, high byte) | чтение старшего байта 16–разрядного слова, непосредственно представленного в команде |

| ORL (operand read, Ion byte) | чтение младшего байта 16–разрядного слова, непосредственно представленного в команде |

| PRD (port read) | ввод данных из порта |

| PWR (port write) | вывод данных в порт |

| SRH (stack read, high byte) | чтение из стека старшего байта |

| SRL (stack read, low byte) | чтение из стека младшего байта |

| SWH (stack write, high byte) | запись в стек старшего байта |

| SWL (ataok write, low byte) | запись в стек младшего байта |

| INTA (interrupt .acknowledge) | подтверждение прерывания микропроцессором |

| SPI (stack pointer increment) | инкремент указателя стека в конце цикла |

| SPD (atack pointer deorement) | декремент указателя стека в конце цикла |

| (n) | продолжительность цикла в периодах тактовой частоты |

Таблица 5.3. очередность выполнения по циклам

| Тип команды | Байт | Цикл M1 | Цикл M2 | Цикл M3 | Цикл M4 | Цикл M5 | Пояснение |

|---|---|---|---|---|---|---|---|

| LD r1,r2 | 1 | OCR(4) | ii: IX или IY | ||||

| LD r,n | 2 | OCR(4) | ORD(3) | ||||

| LD r,(HL) | 1 | OCR(4) | MRD(3) | ||||

| LD (HL),r | 1 | OCR(4) | MWR(3) | ||||

| LD r,(ii+d) | 3 | CBR(4); OCR(4) | ORD(3) | IOP(5) | MRD(3) | ||

| LD (ii+d),r | 3 | CBR(4); OCR(4) | ORD(3) | IOP(5) | MWR(3) | ||

| LD (HL),n | 2 | OCR(4) | ORD(3) | MWR(3) | |||

| LD A,(BC); LD A,(DE) | 1 | OCR(4) | MRD(3) | ||||

| LD (BC),A; LD (DE),A | 1 | OCR(4) | MWR(3) | ||||

| LD A,(nn) | 3 | OCR(4) | ORL(3) | ORL(3) | MRD(3) | ||

| LD (nn),a | 3 | OCR(4) | ORL(3) | ORL(3) | MWR(3) | ||

| LD A,i | 2 | CBR(4); OCR(5) | i: I или R | ||||

| LD i,A | 2 | CBR(4); OCR(5) | i: I или R | ||||

| LD dd,nn | 3 | OCR(4) | ORL(3) | ORL(3) | |||

| LD ii,nn | 4 | CBR(4); OCR(4) | ORL(3) | ORL(3) | ii: IX или IY | ||

| LD HL,(nn) | 3 | OCR(4) | ORL(3) | ORL(3) | MRL(3) | MRL(3) | |

| LD (nn),HL | 3 | OCR(4) | ORL(3) | ORL(3) | MWL(3) | MWL(3) | |

| LD dd,(nn) | 4 | CBR(4); OCR(4) | ORL(3) | ORL(3) | MRL(3) | MRL(3) | |

| LD (nn),dd | 4 | CBR(4); OCR(4) | ORL(3) | ORL(3) | MWL(3) | MWL(3) | |

| LD ii,(nn) | 4 | CBR(4); OCR(4) | ORL(3) | ORL(3) | MRL(3) | MRL(3) | ii: IX или IY |

| LD (nn),ii | 4 | CBR(4); OCR(4) | ORL(3) | ORL(3) | MWL(3) | MWL(3) | ii: IX или IY |

| LD SP,HL | 1 | OCR(6) | |||||

| LD SP,ii | 2 | OCR(6) | ii: IX или IY | ||||

| PUSH qq | 1 | OCR(5); SPD | SWH(3); SPD | SWL(3) | |||

| PUSH ii | 2 | CBR(4); OCR(5); SPD | SWH(3); SPD | SWL(3) | ii: IX или IY | ||

| POP qq | 1 | OCR(4) | SRL(3); SPI | SRH(3); SPI | |||

| POP ii | 2 | CBR(4); OCR(4) | SRL(3); SPI | SRH(3); SPI | ii: IX или IY | ||

| EX DE,HL | 1 | OCR(4) | |||||

| EX AF,AF’; EXX | 1 | OCR(4) | |||||

| EX (SP),HL | 1 | OCR(4) | SRL(3); SPI | SRH(4) | SWH(3); SPD SWL(5) | ||

| EX (SP),ii | 1 | CBR(4); OCR(4) | SRL(3); SPI | SRH(3) | SWH(3); SPD SWL(5) | ii: IX или IY | |

| LDI; LDD; CPI; CPD | 2 | CBR(4); OCR(4) | MRD(3) | MWR(3) | |||

| LDIR; LDDR; CPIR; CPDR | 2 | CBR(4); OCR(4) | MRD(3) | MWR(3) | IOP(5) | IOP(5) в M4, только когда BC≠0 | |

| ALU r | 1 | OCR(4) | ALU означает: ADD, ADC, SUB, SEC, AND, OR, XOR или CP | ||||

| ALU n | 2 | OCR(4) | ORD(3) | ||||

| ALU (HL) | 1 | OCR(4) | MRD(3) | ||||

| ALU (ii+d) | 3 | CBR(4); OCR(4) | ORD(3) | IOP(5) | MRD(3) | ||

| INC r; DEC r | 1 | OCR(4) | |||||

| INC (HL); DEC (HL) | 1 | OCR(4) | MRD(3) | MWR(3) | |||

| INC (ii+d); DEC (ii+d) | 3 | CBR(4); OCR(4) | ORD(3) | IOP(5) | MRD(4) | MWR(3) | ii: IX или IY |

| DAA | 1 | OCR(4) | |||||

| CPL | 1 | OCR(4) | |||||

| NEG | 2 | CBR(4); OCR(4) | |||||

| CCF; SCF | 1 | OCR(4) | |||||

| NOP; HALT | 1 | OCR(4) | |||||

| DI; EI | 1 | OCR(4) | |||||

| IM0; IM1; IM2 | 2 | CBR(4); OCR(4) | |||||

| ADD HL,dd | 1 | OCR(4) | IOP(4) | IOP(3) | |||

| ADC HL,dd; SBC HL,dd; ADD ii,pp | 2 | CBR(4); OCR(4) | IOP(4) | IOP(3) | ADD ii,pp – это ADD IX,pp или ADD IY,rr | ||

| INC dd; DEC dd | 1 | OCR(6) | |||||

| INC ii; DEC ii | 2 | CBR(4); OCR(6) | ii: IX или IY | ||||

| RLCA; RRCA; RLA; RRA | 1 | OCR(4) | ROT означает: RLC, RL, RRC, RR, SLA,SRA или SRL. | ||||

| ROT r | 2 | CBR(4); OCR(4) | |||||

| ROT (HL) | 2 | CBR(4); OCR(4) | MRD(3) | MWR(3) | |||

| ROT (ii+d) | 4 | CBR(4); CBR(4) | ORD(3) | OCR(5) | MRD(4) | MWR(3) | |

| RLD; RRD | 2 | CBR(4); OCR(4) | MRD(3) | IOP(4) | MWR(3) | ||

| BIT b,r; SET b,r; RES b,r | 2 | CBR(4); OCR(4) | |||||

| BIT b,(HL) | 2 | CBR(4); OCR(4) | MRD(4) | ||||

| SET b,(HL); RES b,(HL) | 2 | CBR(4); OCR(4) | MRD(4) | MWR(3) | |||

| BIT b,(ii+d) | 4 | CBR(4); CBR(4) | ORD(3) | OCR(5) | MRD(4) | ||

| SET b,(ii+d);RES b,(ii+d) | 4 | CBR(4); CBR(4) | ORD(3) | OCR(5) | MRD(4) | MWR(3) | ii: IX или IY |

| JP nn; JP cc,nn | 3 | OCR(4) | ORL(3) | ORH(3) | |||

| JR e | 2 | OCR(4) | ORD(3) | IOP(5) | |||

| JR C,e; JR Z,e; JR NC,e; JR NZ,e | 2 | OCR(4) | ORD(3) | IOP(5) | IOP(5) – при невыполнении условия | ||

| JP (HL) | 1 | OCR(4) | |||||

| JP (ii) | 2 | CBR(4); OCR(4) | ii: IX или IY | ||||

| DJNZ e | 2 | OCR(5) | IOP(5), если B≠0 | ||||

| CALL nn | 3 | OCR(4) | ORL(3) | ORH(4); SPD | SWH(3); SPD | SWL(3) | |

| CALL cc,nn | 3 | OCR(4) | ORL(3) | ORH(4); SPD | SWH(3); SPD | SWL(3) | cc |

| CALL cc,nn | 3 | OCR(4) | ORL(3) | ORH(3) | cc не выполняется | ||

| RET | 1 | OCR(4) | SRL(3); SPI | SRH(3); SPI | |||

| RET cc | 1 | OCR(4) | SRL(3); SPI | SRH(3); SPI | cc | ||

| RET cc | 1 | OCR(4) | cc не выполняется | ||||

| RETI; RETN | 2 | CBR(4); OCR(4) | SRL(3); SPI | SRH(3); SPI | |||

| RST p | 1 | OCR(5); SPD | SWH(3); SPD | SWL(3) | |||

| IN A,(n) | 2 | OCR(4) | ORD(4) | PRD(4) | |||

| IN r,(C); INF | 2 | CBR(4); OCR(4) | PRD(4) | ||||

| INI; IND | 2 | CBR(4); OCR(5) | PRD(4) | MWR(3) | |||

| INIR; INDR | 2 | CBR(4); OCR(5) | PRD(4) | MWR(3) | IOP(5) | IOP(5), если B≠0 | |

| OUT (n),A | 2 | OCR(4) | ORD(4) | PWR(4) | |||

| OUT (C),r | 2 | CBR(4); OCR(4) | PWR(4) | ||||

| OUTI; OUTD | 2 | CBR(4); OCR(5) | MRD(3) | PWR(4) | |||

| OTIR; OTDR | 2 | CBR(4); OCR(5) | MRD(3) | PWR(4) | IOP(5) | IOP(5), если B≠0 | |

| Подтверждение прерывания: | |||||||

| NMI | - | OCR(5); SPD | SWH(3); SPD | SWL(3) | См. рис. 6.4 | ||

| INT, Режим 0 | - | INTA(6); SPD | SWH(3); SPD | SWL(3) | При команде RST p | ||

| - | INTA(6) | ORL(3) | ORH(4); SPD | SWH(3); SPD | SWL(3) | При команде CALL | |

| INT, Режим 1 | - | INTA(7;) SPD | SWH(3); SPD | SWL(3) | RST 38H | ||

| INT, Режим 2 | - | INTA(7); SPD | SWH(3); SPD | SWL(3) | MRL(3) | MRH(3) | См. рис. 6.13 |

Принятые обозначения отражают программную суть происходящих в данном цикле действий. С точки зрения процессов на шинах все они сводятся к машинным циклам, рассмотренным в главе 4:

| OCR, CBR | цикл извлечения кода операции (рис. 4.2) |

| MRD, MRH, MRL, ORD, ORH, ORL, SRH, SRL | цикл чтения из памяти (рис. 4.4) |

| MWR, MWH, MWL, SWH, SWL | цикл записи в память (рис. 4.4) |

| PRD | цикл ввода (рис. 4.6) |

| PWR | цикл вывода (рис. 4.6) |

| INTA | цикл подтверждения маскируемого прерывания (рис. 4.9) |